# Intel<sup>®</sup> Itanium<sup>®</sup> 2 Processor

**Hardware Developer's Manual**

**July 2002**

Document Number: 251109-001

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Itanium 2 processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://developer.intel.com/design/litcentr.

Intel and Itanium are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

Copyright © 2002, Intel Corporation. All rights reserved.

\*Other names and brands may be claimed as the property of others.

I2C is a two-wire communication bus /protocol developed by Phillips. SMBus is a subset of the I2C bus/protocol developed by Intel. Implementation of the I2C bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Phillips Electronics, N.V. and North American Phillips Corporation.

# int<sub>el</sub>。 Contents

| 1 | Introd | duction                                          | 1-1  |

|---|--------|--------------------------------------------------|------|

|   | 1.1    | Itanium <sup>®</sup> 2 Processor System Bus      | 1-1  |

|   | 1.2    | Processor Abstraction Layer                      |      |

|   | 1.3    | Terminology                                      |      |

|   | 1.4    | Reference Documents                              |      |

|   |        | 1.4.1 Revision History                           | 1-3  |

| 2 | Itaniu | m <sup>®</sup> 2 Processor Microarchitecture     | 2-1  |

|   | 2.1    | Overview                                         | 2-1  |

|   | 2      | 2.1.1 6-Wide EPIC Core                           |      |

|   |        | 2.1.2 Processor Pipeline                         |      |

|   |        | 2.1.3 Processor Block Diagram                    |      |

|   | 2.2    | Instruction Processing                           |      |

|   |        | 2.2.1 Instruction Prefetch and Fetch             |      |

|   |        | 2.2.2 Branch Prediction                          |      |

|   |        | 2.2.3 Dispersal Logic                            |      |

|   | 2.3    | Execution                                        |      |

|   |        | 2.3.1 Floating-Point Unit (FPU)                  |      |

|   |        | 2.3.2 Integer Logic                              |      |

|   |        | 2.3.3 Register Files                             |      |

|   |        | 2.3.4 Register Stack Engine (RSE)                |      |

|   | 2.4    | Control                                          |      |

|   | 2.5    | Memory Subsystem                                 |      |

|   |        | 2.5.1 L1 Instruction Cache                       |      |

|   |        | 2.5.2 L1 Data Cache                              |      |

|   |        | 2.5.3 Unified L2 Cache                           |      |

|   |        | 2.5.4 Unified L3 Cache                           |      |

|   |        | 2.5.5 The Advanced Load Address Table (ALAT)     |      |

|   |        | 2.5.6 Translation Lookaside Buffers (TLBs)       |      |

|   |        | 2.5.7 Cache Coherency                            |      |

|   |        | 2.5.8 Write Coalescing                           |      |

|   |        | 2.5.9 Memory Ordering                            | 2-11 |

|   | 2.6    | IA-32 Execution                                  | 2-11 |

| 3 | Syste  | m Bus Overview                                   | 3-1  |

|   | 3.1    | Signaling on the Itanium® 2 Processor System Bus | 3-1  |

|   |        | 3.1.1 Common Clock Signaling                     | 3-1  |

|   |        | 3.1.2 Source Synchronous Signaling               |      |

|   | 3.2    | Signal Overview                                  | 3-3  |

|   |        | 3.2.1 Control Signals                            | 3-4  |

|   |        | 3.2.2 Arbitration Signals                        | 3-4  |

|   |        | 3.2.3 Request Signals                            | 3-5  |

|   |        | 3.2.4 Snoop Signals                              | 3-5  |

|   |        | 3.2.5 Response Signals                           |      |

|   |        | 3.2.6 Data Signals                               |      |

|   |        | 3.2.7 Defer Signals                              |      |

|   |        | 3.2.8 Error Signals                              |      |

|   |        | 3.2.9 Execution Control Signals                  |      |

# intel

|   |         |            | IA-32 Compatibility Signals                           |      |

|---|---------|------------|-------------------------------------------------------|------|

|   |         |            | Platform Signals                                      |      |

|   |         | 3.2.12     | Diagnostic Signals                                    | 3-10 |

| 4 | Data I  | ntegrity   |                                                       | 4-1  |

|   | 4.1     | Error C    | lassification                                         | 4-1  |

|   | 4.2     |            | ® 2 Processor System Bus Error Detection              |      |

|   |         | 4.2.1      | Bus Signals Protected Directly                        |      |

|   |         | 4.2.2      | Bus Signals Protected Indirectly                      |      |

|   |         | 4.2.3      | Unprotected Bus Signals                               |      |

|   |         | 4.2.4      | Itanium® 2 Processor System Bus Error Code Algorithms | 4-3  |

| 5 | Config  | guration a | nd Initialization                                     | 5-1  |

|   | 5.1     | Configu    | uration Overview                                      | 5-1  |

|   | 5.2     |            | uration Features                                      |      |

|   | 0.2     | 5.2.1      | Data Bus Error Checking                               |      |

|   |         | 5.2.2      | Response/ID Signal Parity Error Checking              |      |

|   |         | 5.2.3      | Address/Request Signal Parity Error Checking          |      |

|   |         | 5.2.4      | BERR# Assertion for Initiator Bus Errors              |      |

|   |         | 5.2.5      | BERR# Assertion for Target Bus Errors                 |      |

|   |         | 5.2.6      | BERR# Sampling                                        |      |

|   |         | 5.2.7      | BINIT# Error Assertion                                | 5-3  |

|   |         | 5.2.8      | BINIT# Error Sampling                                 | 5-3  |

|   |         | 5.2.9      | In-Order Queue Pipelining                             | 5-3  |

|   |         | 5.2.10     | Request Bus Parking Enabled                           | 5-3  |

|   |         | 5.2.11     | Symmetric Agent Arbitration ID                        | 5-4  |

|   |         |            | Clock Frequency Ratios                                |      |

|   | 5.3     |            | ation Overview                                        |      |

|   |         | 5.3.1      | Initialization with RESET#                            |      |

|   |         | 5.3.2      | Initialization with INIT                              | 5-6  |

| 6 | Test A  | Access Po  | ort (TAP)                                             | 6-1  |

|   | 6.1     | Interfac   | ce                                                    | 6-2  |

|   | 6.2     | Access     | ing The TAP Logic                                     | 6-2  |

|   | 6.3     | TAP Re     | egisters                                              | 6-4  |

|   | 6.4     | TAP Ins    | structions                                            | 6-4  |

|   | 6.5     | Reset E    | Behavior                                              | 6-5  |

| 7 | Integra | ation Too  | ls                                                    | 7-1  |

|   | 7.1     | In-Targ    | et Probe (ITP)                                        | 7-1  |

|   | 7.2     |            | nalyzer Interface (LAI)                               |      |

| Α | Signa   | ls Referer | nce                                                   | A-1  |

|   | A.1     |            | etical Signals Reference                              |      |

|   | 74.1    | A.1.1      | A[49:3]# (I/O)                                        |      |

|   |         |            | A20M# (I)                                             |      |

|   |         | A.1.3      | ADS# (I/O)                                            |      |

|   |         | A.1.4      | AP[1:0]# (I/O)                                        |      |

|   |         | A.1.5      | ASZ[1:0]# (I/O)                                       |      |

|   |         | A.1.6      | ATTR[3:0]# (I/O)                                      |      |

|   |         | A.1.7      | BCLKp/BCLKn (I)                                       |      |

|   |         | A.1.8      | BE[7:0]# (I/O)                                        |      |

# intها.

| A.1.9  | BERR# (I/O)                     | A-3 |

|--------|---------------------------------|-----|

| A.1.10 | BINIT# (I/O)                    | A-4 |

| A.1.11 | BNR# (I/O)                      | A-4 |

| A.1.12 | BPM[5:0]# (I/O)                 | A-4 |

| A.1.13 | BPRI# (I)                       | A-4 |

| A.1.14 | BR[0]# (I/O) and BR[3:1]# (I)   | A-4 |

| A.1.15 | BREQ[3:0]# (I/O)                | A-5 |

| A.1.16 | CCL# (I/O)                      | A-6 |

| A.1.17 | CPUPRES# (O)                    | A-6 |

| A.1.18 | D[127:0]# (I/O)                 | A-6 |

| A.1.19 | D/C# (I/O)                      | A-6 |

| A.1.20 | DBSY# (I/O)                     | A-6 |

| A.1.21 | DBSY_C1# (O)                    | A-6 |

| A.1.22 | DBSY_C2# (O)                    | A-6 |

| A.1.23 | DEFER# (I)                      | A-7 |

| A.1.24 | DEN# (I/O)                      | A-7 |

| A.1.25 | DEP[15:0]# (I/O)                | A-7 |

| A.1.26 | DHIT# (I)                       | A-7 |

| A.1.27 | • • •                           |     |

| A.1.28 | DRDY# (I/O)                     | A-8 |

| A.1.29 | DRDY_C1# (O)                    | A-8 |

| A.1.30 | DRDY_C2# (O)                    |     |

| A.1.31 | DSZ[1:0]# (I/O)                 |     |

| A.1.32 | EXF[4:0]# (I/O)                 |     |

|        | FCL# (I/O)                      |     |

|        | FERR# (O)                       |     |

| A.1.35 | GSEQ# (I)                       |     |

| A.1.36 | HIT# (I/O) and HITM# (I/O)      | A-9 |

| A.1.37 | ID[9:0]# (Í)                    |     |

| A.1.38 | IDS# (I)                        | A-9 |

| A.1.39 | IGNNE# (I)                      |     |

| A.1.40 | INIT# (I)                       |     |

| A.1.41 | INT (I)                         |     |

| A.1.42 | IP[1:0]# (I)                    |     |

|        | LEN[2:0]# (I/O)                 |     |

|        | LINT[1:0] (I)                   |     |

|        | LOCK# (I/O)                     |     |

|        | NMI (I)                         |     |

|        | OWN# (I/O)                      |     |

|        | PMI# (I)                        |     |

|        | PWRGOOD (I)                     |     |

|        | REQ[5:0]# (I/O)                 |     |

|        | RESET# (I)                      |     |

|        | RP# (I/O)                       |     |

|        | RS[2:0]# (I)                    |     |

|        | RSP# (I)                        |     |

|        | SBSY# (I/O)                     |     |

|        | SBSY_C1# (O)                    |     |

|        | SBSY_C2# (O)                    |     |

|        | SPLCK# (I/O)                    |     |

|        | STBn[7:0]# and STBp[7:0]# (I/O) |     |

# int<sub>el®</sub>

|                |      | A.1.60 TCK (I)                                                             | A-14  |

|----------------|------|----------------------------------------------------------------------------|-------|

|                |      | A.1.61 TDI (I)                                                             | A-14  |

|                |      | A.1.62 TDO (O)                                                             | A-14  |

|                |      | A.1.63 THRMTRIP# (O)                                                       | A-14  |

|                |      | A.1.64 THRMALERT# (O)                                                      | A-15  |

|                |      | A.1.65 TMS (I)                                                             | A-15  |

|                |      | A.1.66 TND# (I/O)                                                          | A-15  |

|                |      | A.1.67 TRDY# (I)                                                           | A-15  |

|                |      | A.1.68 TRST# (I)                                                           | A-15  |

|                |      | A.1.69 WSNP# (I/O)                                                         | A-15  |

|                | A.2  | Signal Summaries                                                           | A-15  |

| <b>Figures</b> | 3    |                                                                            |       |

|                | 2-1  | Two Examples Illustrating Supported Parallelism                            | 2-2   |

|                | 2-2  | Itanium® 2 Processor Core Pipeline                                         |       |

|                | 2-3  | Itanium® 2 Processor Block Diagram                                         | 2-4   |

|                | 2-4  | Itanium® 2 Processor FMAC Units                                            | 2-6   |

|                | 2-5  | Itanium® 2 Processor Cache Hierarchy                                       | 2-8   |

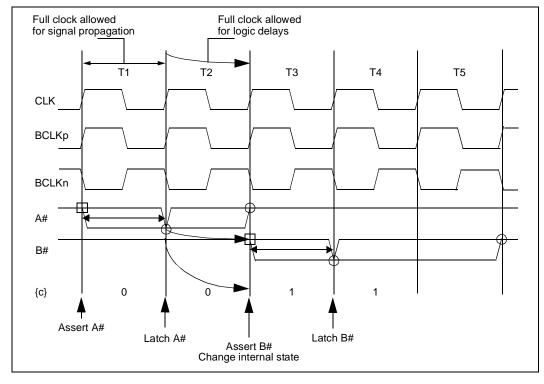

|                | 3-1  | Common Clock Latched Protocol                                              | 3-2   |

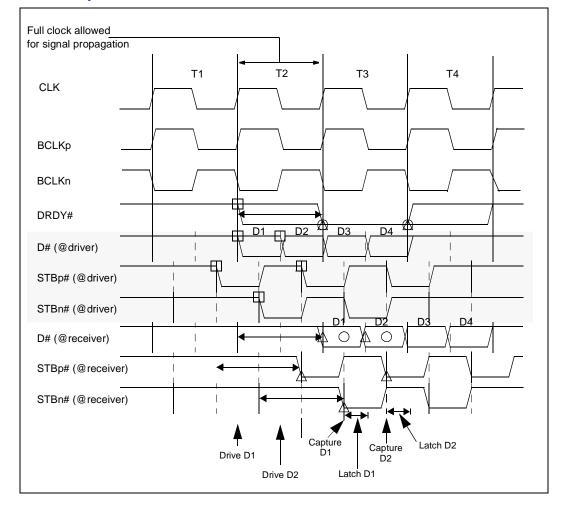

|                | 3-2  | Source Synchronous Latched Protocol                                        | 3-3   |

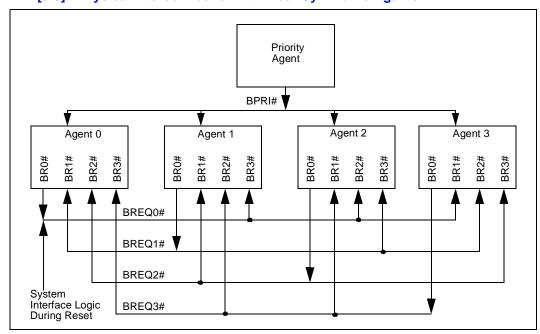

|                | 5-1  | BR[3:0]# Physical Interconnection with Four Symmetric Agents               |       |

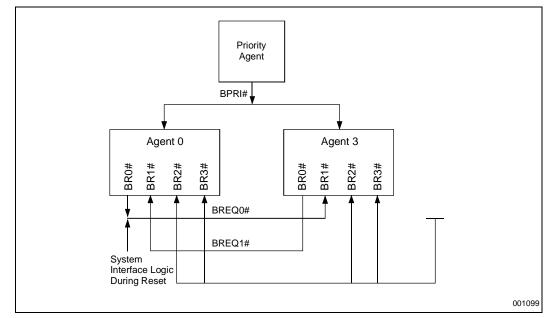

|                | 5-2  | BR[3:0]# Physical Interconnection with Two Symmetric Agents                | 5-5   |

|                | 6-1  | Test Access Port Block Diagram                                             | 6-1   |

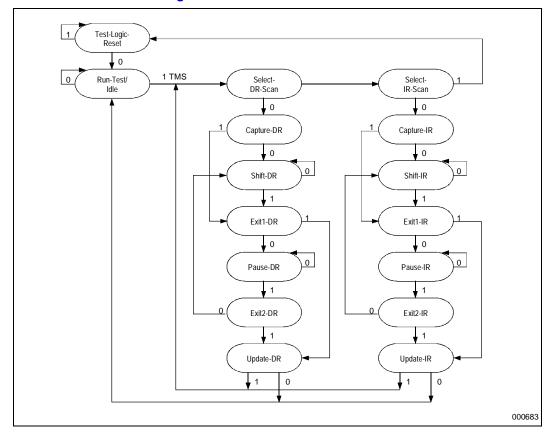

|                | 6-2  | TAP Controller State Diagram                                               | 6-2   |

|                |      |                                                                            |       |

| Tobles         |      |                                                                            |       |

| Tables         |      |                                                                            |       |

|                | 3-1  | Control Signals                                                            |       |

|                | 3-2  | Arbitration Signals                                                        |       |

|                | 3-3  | Request Signals                                                            |       |

|                | 3-4  | Snoop Signals                                                              |       |

|                | 3-5  | Response Signals                                                           |       |

|                | 3-6  | Data Signals                                                               |       |

|                | 3-7  | STBp[7:0]# and STBn[7:0]# Associations                                     |       |

|                | 3-8  | Defer Signals                                                              |       |

|                | 3-9  | Error Signals                                                              |       |

|                | 3-10 | Execution Control Signals                                                  |       |

|                | 3-11 | Platform Signals                                                           |       |

|                | 3-12 | Diagnostic Signals                                                         |       |

|                | 4-1  | Direct Bus Signal Protection                                               |       |

|                | 5-1  | Power-On Configuration Features                                            |       |

|                | 5-2  | Itanium® 2 Processor Bus BREQ[3:0]# Interconnect (4-Way Processors)        |       |

|                | 5-3  | Itanium® 2 Processor Bus BREQ[3:0]# Interconnect (2-Way Processors)        |       |

|                | 5-4  | Arbitration ID Configuration                                               | 5-5   |

|                | 5-5  | Itanium® 2 Processor System Bus to Core Frequency Multiplier Configuration | ո 5-5 |

|                | 5-6  | Itanium® 2 Processor Reset State (after PAL)                               | . 5-6 |

|                | 5-7  | Itanium® Processor INIT State                                              |       |

|                | 6-1  | Instructions for the Itanium <sup>®</sup> 2 Processor TAP Controller       | . 6-4 |

|                |      |                                                                            |       |

# intطِ

| A-1  | Address Space Size                                                | A-2  |

|------|-------------------------------------------------------------------|------|

| A-2  | Effective Memory Type Signal Encoding                             | A-2  |

| A-3  | Special Transaction Encoding on Byte Enables                      | A-3  |

| A-5  | BR0# (I/O), BR1#, BR2#, BR3# Signals for 2P Rotating Interconnect | A-5  |

| A-4  | BR0# (I/O), BR1#, BR2#, BR3# Signals for 4P Rotating Interconnect | A-5  |

| A-6  | BR[3:0]# Signals and Agent IDs                                    | A-5  |

| A-7  | DID[9:0]# Encoding                                                | A-7  |

| A-8  | Extended Function Signals                                         |      |

| A-9  | Length of Data Transfers                                          |      |

| A-10 | Transaction Types Defined by REQa#/REQb# Signals                  |      |

| A-11 | STBp[7:0]# and STBn[7:0]# Associations                            |      |

| A-12 | Output Signals                                                    |      |

| A-13 | Input Signals                                                     | A-16 |

| A-14 | Input/Output Signals (Single Driver)                              |      |

| A-15 | Input/Output Signals (Multiple Driver)                            |      |

# int<sub>el®</sub>

intel®

Introduction

The Intel<sup>®</sup> Itanium<sup>®</sup> 2 processor, the second in a family of processors based on the Itanium architecture, is designed to address the needs of high-performance servers and workstations. The Itanium architecture goes beyond RISC and CISC approaches by employing Explicitly Parallel Instruction Computing (EPIC), which pairs extensive processing resources with intelligent compilers that enable parallel execution explicit to the processor. Its large internal resources combine with predication and speculation to enable optimization for high performance applications running on multiple operating systems, including versions of Microsoft Windows\*, HP-UX\* and Linux\*. The Itanium 2 processor is designed to support very large scale systems, including those employing thousands of processors, to provide the processing power and performance head room for the most demanding enterprise and technical computing applications. SMBus compatibility and comprehensive reliability, availability and serviceability (RAS) features make the Itanium 2 processor ideal for applications requiring high up-time. For high performance servers and workstations, the Itanium 2 processor offers outstanding performance and reliability for today's applications and the scalability to address the growing e-business needs of tomorrow.

#### Itanium® 2 Processor System Bus 1.1

Most Itanium 2 processor signals use the Itanium processor's Assisted Gunning Transceiver Logic (AGTL+) signaling technology. The termination voltage, V<sub>CTERM</sub>, is generated on the baseboard and is the system bus high reference voltage. The buffers that drive most of the system bus signals on the Itanium 2 processor are actively driven to V<sub>CTERM</sub> during a low-to-high transition to improve rise times and reduce noise. These signals should still be considered open-drain and require termination to V<sub>CTERM</sub> which provides the high level. When on-die termination is enabled, the Itanium 2 system bus is terminated to  $V_{CTERM}$  through active termination within the bus agents at each end of the bus. There is also support of off-die termination in which case the termination is provided by external resistors connected to V<sub>CTERM</sub>.

AGTL+ inputs use differential receivers which require a reference signal (V<sub>REF</sub>). V<sub>REF</sub> is used by the receivers to determine if a signal is a logical 0 or a logical 1. The Itanium 2 processor generates V<sub>REF</sub> on-die, thereby eliminating the need for an off-chip reference voltage source.

#### **Processor Abstraction Layer** 1.2

The Itanium 2 processor requires implementation-specific Processor Abstraction Layer (PAL) firmware. PAL firmware supports processor initialization, error recovery, and other functionality. It provides a consistent interface to system firmware and operating systems across processor hardware implementations. The Intel<sup>®</sup> Itanium<sup>TM</sup> Architecture Software Developer's Manual, Volume 2: System Architecture, describes PAL. Platforms must provide access to the firmware address space and PAL at reset to allow Itanium 2 processors to initialize.

The System Abstraction Layer (SAL) firmware contains platform-specific firmware to initialize the platform, boot to an operating system, and provide runtime functionality. Further information about SAL is available in the Itanium Processor Family System Abstraction Layer Specification.

# 1.3 Terminology

In this document, a '#' symbol after a signal name refers to an active low signal. This means that a signal is in the active state (based on the name of the signal) when driven to a low level. For example, when RESET# is low, a processor reset has been requested. When NMI is high, a non-maskable interrupt has occurred. In the case of lines where the name does not imply an active state but describes part of a binary sequence (such as address or data), the '#' symbol implies that the signal is inverted. For example, D[3:0] = 'HLHL' refers to a hex 'A', and D [3:0] # = 'LHLH' also refers to a hex 'A' (H = High logic level, L = Low logic level).

In many cases, signals are mapped one-to-one to physical pins with the same names. In other cases, different signals are mapped onto the same pin. For example, this is the case with the address pins A[49:3]#. During the first clock, the address pins are asserted indicating a valid address. The first clock is indicated by the lower case a, or just the pin name itself: Aa[49:3]# or A[49:3]#. During the second clock, other information is asserted on the address pins. These signals are referenced either by their functional signal names, such as DID[9:0]#, or by using a lower case b with the pin name, such as Ab[25:16]#. Note also that several pins have configuration functions at the asserted to deasserted edge of RESET#.

The term "system bus" refers to the interface between the processor, system core logic and other bus agents. The system bus is a multiprocessing interface to processors, memory and I/O.

A signal name has all capitalized letters, e.g. VCTERM.

A symbol referring to a voltage level, current level, or a time value carries a plain subscript, e.g.  $V_{CC,core}$ , or a capitalized abbreviated subscript, e.g.  $T_{CO}$ .

#### 1.4 Reference Documents

The reader of this specification should also be familiar with material and concepts presented in the following documents:

| Title                                                                                                          | Document Number            |

|----------------------------------------------------------------------------------------------------------------|----------------------------|

| Intel <sup>®</sup> Itanium <sup>®</sup> 2 Processor at 1.0 GHz and 900 MHz Datasheet                           | 250945                     |

| Intel® Itanium® 2 Processor Specification Update                                                               | 251141                     |

| Intel <sup>®</sup> Itanium™ Architecture Software Developer's Manual                                           |                            |

| Volume 1: Application Architecture                                                                             | 245317                     |

| Volume 2: System Architecture                                                                                  | 245318                     |

| Volume 3: Instruction Set Reference                                                                            | 245319                     |

| Intel® Itanium® 2 Processor BSDL Model                                                                         |                            |

| Intel <sup>®</sup> Itanium <sup>®</sup> 2 Processor Reference Manual for Software Development and Optimization | 251110                     |

| Intel <sup>®</sup> Itanium™ Processor Family System Abstraction Layer Specification                            | 245359                     |

| Intel <sup>®</sup> Itanium™ Processor Family Error Handling Guide                                              | 249278                     |

| ITP700 Debug Port Design Guide                                                                                 | 249679                     |

| System Management Bus Specification                                                                            | http://www.smbus.org/specs |

Contact your Intel representative or check http://developer.intel.com for the latest revision of the reference documents.

# 1.4.1 Revision History

| Versio<br>Number | Description                       | Date      |

|------------------|-----------------------------------|-----------|

| 001              | Initial release of this document. | July 2002 |

Introduction

# intel® Itanium® 2 Processor Microarchitecture

This chapter provides an introduction to the Itanium 2 processor microarchitecture. For detailed information on Itanium architecture, please refer to the *Intel*<sup>®</sup> *Itanium*™ *Architecture Software* Developer's Manual.

#### 2.1 **Overview**

The Itanium 2 processor is the second implementation of the Itanium Instruction Set Architecture (ISA). The processor employs EPIC design concepts for a tighter coupling between hardware and software. In this design style, the interface between hardware and software is designed to enable the software to exploit all available compile-time information, and efficiently deliver this information to the hardware. It addresses several fundamental performance bottlenecks in modern computers, such as memory latency, memory address disambiguation, and control flow dependencies. The EPIC constructs provide powerful architectural semantics, and enable the software to make global optimizations across a large scheduling scope, thereby exposing available Instruction Level Parallelism (ILP) to the hardware. The hardware takes advantage of this enhanced ILP, and provides abundant execution resources. Additionally, it focuses on dynamic runtime optimizations to enable the compiled code schedule to flow through at high throughput. This strategy increases the synergy between hardware and software, and leads to higher overall performance.

The Itanium 2 processor provides a 6-wide, 8-stage deep pipeline running at either 1.0 GHz or 900 MHz. This provides a combination of both abundant resources to exploit ILP as well as increased frequency for minimizing the latency of each instruction. The resources consist of six integer units, six multimedia units, two load and two store units, three branch units, two extended-precision floating-point units, and two additional single-precision floating-point units. The hardware employs dynamic prefetch, branch prediction, a register scoreboard, and non-blocking caches. Three levels of on-die cache minimize overall memory latency. This includes either a 3 MB or 1.5MB L3 cache, accessed at core speed, providing over 32 GB/cycle of data bandwidth. The system bus is designed for glueless MP support for up to 4 processors per system bus, and can be used as an effective building block for very large systems. The balanced core and memory subsystem provide high performance for a wide range of applications ranging from commercial workloads to high performance technical computing.

#### 2.1.1 6-Wide EPIC Core

The Itanium 2 processor provides a 6-wide, 8-stage deep pipeline, based on the EPIC design. The pipelines utilize the following execution units: six Integer ALUs, six Multimedia ALUs, two Extended Precision Floating-point Units, two additional Single Precision Floating-point Units, two Load and two Store Units, and three Branch Units. The machine is capable of fetching, issuing, executing, and retiring six instructions, or two instructions bundles, per clock.

An instruction bundle contains three instructions and a template indicator, assigned by the compiler. Each instruction in the bundle is eventually dispersed into one of the execution pipelines according to its type: ALU Integer (A), Non-ALU Integer (I), Memory (M), Floating-point (F), Branch (B), or Extended (L). The Itanium 2 processor's increase in execution units more than

triples the dispersal options for the compiler over the Itanium processor. Please refer to the  $Intel^{\textcircled{B}}$   $Itanium^{\textcircled{TM}}$  Architecture Software Developer's Manual for more information regarding instructions and bundles, and the  $Intel^{\textcircled{B}}$   $Itanium^{\textcircled{B}}$  2 Processor Reference Manual for Software Development and Optimization for more information regarding Itanium 2 processor instruction dispersal.

Figure 2-1 illustrates two examples demonstrating the level of parallel operation supported for various workloads. For enterprise and commercial codes, the MII/MBB template combination in a bundle pair provides six instructions or eight parallel ops per clock (two load/store, two general-purpose ALU ops, two post-increment ALU ops, and two branch instructions). Alternatively, an MIB/MIB pair allows the same mix of operations, but with one branch hint and one branch op, instead of two branch ops. For scientific code, the use of the MFI template in each bundle enables twelve parallel Ops per clock (loading four double-precision operands to the registers, executing four double-precision flops, two integer ALU ops and two post-increment ALU ops). For digital content creation codes that use single precision floating-point, the SIMD features in the machine effectively provide the capability to perform up to twenty parallel ops per clock (loading eight single precision operands, executing eight single precision FLOPs, two integer ALUs, and two post-incrementing ALU operations).

6 Instructions Provide: М M 12 Parallel Ops/Clock for Scientific Computing 20 Parallel Ops/Clock for Digital Content Load 4 DP (8 SP) 4 DP FLOPS 2 ALU Ops Ops via 2 Fld-pair (8 SP FLOPS) 2 ALU Ops (Post 6 Instructions Provide: Μ 8 Parallel Ops/Clock for Enterprise and Internet Applications 2 Branch Insts. 2 Loads + 2 ALU Ops 2 ALU Ops (Post incr.) SP - Single Precision DP - Double Precision 001246

Figure 2-1. Two Examples Illustrating Supported Parallelism

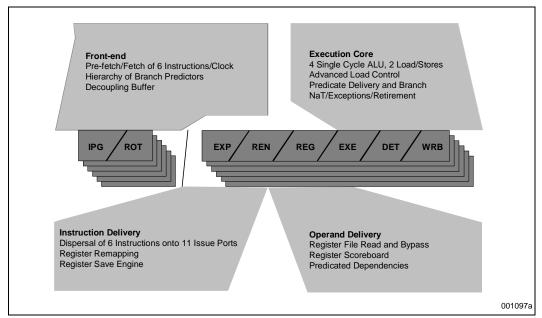

# 2.1.2 Processor Pipeline

The processor hardware is organized into a eight stage core pipeline, shown in Figure 2-2, that can execute up to six instructions in parallel per clock. The first two pipeline stages perform the instruction fetch and deliver the instructions into a decoupling buffer in the instruction rotation (ROT) stage that enables the front-end of the machine to operate independently from the back end. The bold line in the middle of the core pipeline indicates a point of decoupling. Dispersal and register renaming are performed in the next two stages, expand (EXP) and register rename (REN). Operand delivery is accomplished across the register read (REG) stage, where the register file is accessed and data is delivered through the bypass network after processing the predicate control. Finally, the last three stages perform the wide parallel execution followed by exception management and retirement. In particular, the exception detection (DET) stage accommodates branch resolution as well as memory exception management and speculation support.

Please see the *Intel*<sup>®</sup> *Itanium*<sup>®</sup> 2 *Processor Reference Manual for Software Development and Optimization* for more information the Itanium 2 processor pipeline.

Figure 2-2. Itanium® 2 Processor Core Pipeline

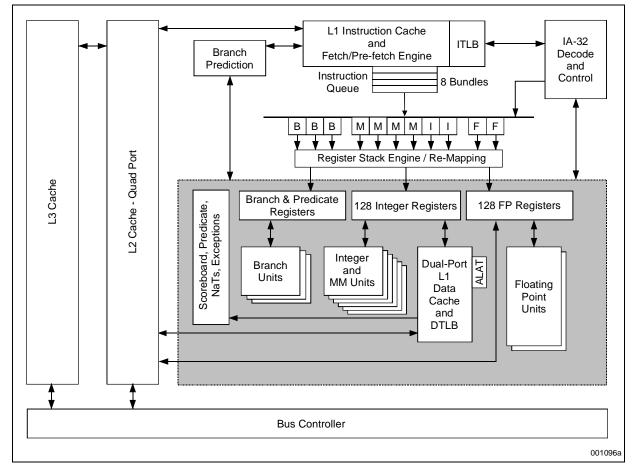

# 2.1.3 Processor Block Diagram

Figure 2-3 shows a block diagram of the Itanium 2 processor. The function of the processor is divided into five groups, each summarized below. The following sections give a high-level description of the operation of each group.

#### 1. Instruction Processing

The instruction processing block contains the logic for instruction prefetch, instruction fetch, L1 instruction cache, branch prediction, instruction address generation, instruction buffers, instruction issue, dispersal and rename.

#### 2. Execution

The execution block consists of the multimedia logic, integer ALU execution logic, floating-point (FP) execution logic, integer register file, L1 data cache and FP register file.

#### 3. Control

The control block consists of the exception handler and the pipeline control, as well as the Register Stack Engine (RSE).

#### 4. Memory Subsystem

The memory subsystem contains the unified L2 cache, on-chip L3 cache, Programmable Interrupt Controller (PIC), instruction and data Translation Lookaside Buffers (TLB), Advanced Load Address Table (ALAT) and external system bus interface logic.

#### 5. IA-32 Compatibility Execution Engine

Instructions for IA-32 applications are fetched, decoded and scheduled for execution by the IA-32 compatibility execution engine.

Figure 2-3. Itanium<sup>®</sup> 2 Processor Block Diagram

# 2.2 Instruction Processing

#### 2.2.1 Instruction Prefetch and Fetch

The Itanium 2 processor speculatively prefetches instructions from a pipelined cache into a decoupling buffer. The Itanium 2 processor uses a sophisticated branch prediction strategy and compiler hints for speculative prefetches. The instruction sequencing portion of the Itanium 2 processor is responsible for fetching and dispersing instructions to the execution units. The instruction address generation unit selects the next instruction pointer (IP). The instruction pointer is selected between the next sequential address, static and dynamic branch prediction addresses, instruction addresses delivered by the compatibility logic, validated target and address to correct for mispredicted branches, or the address of exception handlers.

The Itanium 2 processor reads two instruction bundles (three instructions per bundle) from the L1 instruction cache (L1I) and places them in the instruction buffers. The instruction buffers store bundles of instructions waiting to be consumed by the execution units. To reduce the effect of branch prediction bubbles caused by instruction cache misses, bundles read from the instruction buffers are sent to the instruction issue and rename logic based on the availability of execution resources.

#### 2.2.2 Branch Prediction

The branch prediction logic uses advanced prediction schemes to anticipate the direction and target of each branch read from the instruction cache. The Itanium 2 processor features a 0-bubble branch prediction algorithm and a backup branch prediction table. Whenever a branch happens, the branch target will be restored to the instruction pointer generation logic.

The instruction prefetch logic serves as the interface between the L1I and L2 cache. It prefetches instructions from L2 before they are needed in order to prevent L1I misses. Prefetching is executed under control of the compiler. If an L1 instruction cache miss does occur, it will stall the instruction address generation logic and retrieve the information from the L2 cache. If the instruction does not reside in L2 cache, it will proceed to check the L3 cache.

# 2.2.3 Dispersal Logic

There are twelve templates for Itanium instructions. A template contains explicit stop bits to indicate to the hardware to stop parallel issue of subsequent instructions. There are three instructions per bundle and the hardware can handle two bundles (i.e. six instructions) per clock. The dispersal logic sends each instruction to one of the fully pipelined functional units through its issue ports.

The instruction buffer holds a maximum of eight instruction bundles. The buffer can present two bundles to the dispersal logic every cycle. In general, instructions are routed to a supporting execution port on a first available basis.

# 2.3 Execution

The Itanium 2 processor execution logic consists of six multimedia units, six integer units, two floating-point units, three branch units and four load/store units. The Itanium 2 processor has general registers and FP registers to manage work in progress. Integer loads are processed by the L1 data cache but integer stores will be processed by L2. FP loads and stores are also processed by the L2 cache. Whenever a lookup occurs in L1, a speculative request is sent to the L2 cache.

The multimedia engines treat the 64-bit data as 2 x 32-bit, 4 x 16-bit or 8 x 8-bit packed data types. Three classes of arithmetic operations can be performed on the packed or Single Instruction Multiple Data (SIMD) data types: arithmetic, shift and data arrangement. Meanwhile the integer engines support up to six non-packed integer arithmetic and logical operations. Up to six integer or multimedia operations can be executed each cycle.

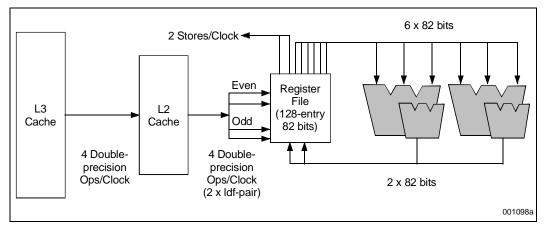

# 2.3.1 Floating-Point Unit (FPU)

The Itanium 2 processor provides high floating-point execution bandwidth. The Itanium 2 processor FPU has four pipeline stages. Extra bypassing logic allows quick data forwarding from various FP stages to the FP write back stage. The FP logic also includes an FP Multiply Accumulate (FMAC) hardware unit, fast rounding logic and support for SIMD formats. The Itanium 2 processor can issue up to two FP instructions, or two Integer multiplications, plus two FP loads and two FP stores (or four FP loads) instructions every clock cycle.

Numeric operands are checked for possible numeric exceptions before the instruction enters the FP pipeline. Results are written back at the end of the pipeline.

The FPU supports two FMACs that operate on 82-bit values. The FMACs can execute single, double and double-extended precision FP operations. The FPU has a 128-entry FP register file with eight read and at least six write ports. The FP registers can support four double precision loads every clock from memory, two 82-bit writebacks from the FMACs and two store operations for the two parallel extended precision FMACs every clock. Refer to Figure 2-4 for a diagram of the FMAC units.

Figure 2-4. Itanium® 2 Processor FMAC Units

# 2.3.2 Integer Logic

The six integer execution units execute 64-bit arithmetic, logical, shift and bit-field manipulation instructions. Additionally it can execute instructions to accelerate operations on 32-bit pointers. Other operations include computing predicates, linear addresses and flag generation for the IA-32 compatible engine.

The integer logic has six general purpose ALUs and two load and two store ports. The ALUs have full bypassing capability.

# 2.3.3 Register Files

The Itanium 2 processor implements the massive register resources provided by the Itanium architecture. The large number of registers allow many operations to complete without reading from or writing to memory. The primary execution registers include: 128 general registers, 128 floating-point registers, 64 predicate registers, and 8 branch registers.

## 2.3.3.1 General Registers

A set of 128 (64-bit) general registers provide the central resource for all integer and integer multimedia computation. They are numbered GR0 through GR127, and are available to all programs at all privilege levels.

The general registers are partitioned into two subsets. General registers 0 through 31 are termed the static general registers. Of these, GR0 is special in that it always reads as zero when sourced as an operand, and attempting to write to GR0 causes an Illegal Operation fault. General registers 32 through 127 are termed the stacked general registers. The stacked registers are made available to a program by allocating a register stack frame consisting of a programmable number of local and output registers.

#### 2.3.3.2 Floating-Point Registers

A set of 128 (82-bit) floating-point registers are used for all floating-point computation. They are numbered FR0 through FR127, and are available to all programs at all privilege levels. The floating-point registers are partitioned into two subsets. Floating-point registers 0 through 31 are termed the static floating-point registers. Of these, FR0 and FR1 are special. FR0 always reads as +0.0 when sourced as an operand, and FR1 always reads as +1.0. When either of these is used as a destination, a fault is raised.

Floating-point registers 32 through 127 are termed the rotating floating-point registers. These registers can be programmatically renamed to accelerate loops.

# 2.3.3.3 Predicate Registers

A set of 64 (1-bit) predicate registers are used to hold the results of compare instructions. These registers are numbered PR0 through PR63, and are available to all programs at all privilege levels. These registers are used for conditional execution of instructions.

The predicate registers are partitioned into two subsets. Predicate registers 0 through 15 are termed the static predicate registers. Of these, PR0 always reads as '1' when sourced as an operand, and when used as a destination, the result is discarded. The static predicate registers are also used in conditional branching.

Predicate registers 16 through 63 are termed the rotating predicate registers. These rotating registers support efficient software pipeline loops.

#### 2.3.3.4 Branch Registers

A set of 8 (64-bit) branch registers are used to hold branching information. They are numbered BR0 through BR7, and are available to all programs at all privilege levels. The branch registers are used to specify the branch target addresses for indirect branches.

# 2.3.4 Register Stack Engine (RSE)

The Itanium ISA avoids the spilling and filling of registers at procedure interfaces through a large register file and a mechanism for accessing the registers through an indirection base. The indirection mechanism allows stacking of register frames and sharing of inter-procedure variables through the register file.

When a procedure is called, a new frame of registers is made available to the called procedure without the need for an explicit save of the callers' registers. The old registers remain in the large on-chip physical register file as long as there is enough physical capacity. When the number of registers needed overflows the available physical capacity, a state machine called the Register Stack Engine (RSE) saves the registers to memory to free up the necessary registers needed for the upcoming call. The RSE maintains the illusion of an infinite number of registers.

On a call return, the base register is restored to the value that the caller was using to access registers prior to the call. Often a return is encountered even before these registers need to be saved, making it unnecessary to restore them. In cases where the RSE has saved some of the callee's registers, the processor stalls on return until the RSE can restore the appropriate number of the callee's registers. The Itanium 2 processor implements the forced lazy mode of the RSE, as described in the Intel® Itanium® 2 Processor Reference Manual for Software Development and Optimization.

The Intel<sup>®</sup> Itanium<sup>TM</sup> Architecture Software Developer's Manual describes the RSE in more detail.

#### 2.4 Control

The control section of the Itanium 2 processor is made up of the exception handler and pipeline control. The exception handler implements exception prioritizing. Pipeline control has a scoreboard to detect register source dependencies and a cache to support data speculation. The machine stalls only when source operands are not yet available. Pipeline control supports predication via predication registers.

The pipeline control section also contains a Performance Monitoring Unit designed to collect data that can be dumped for analyzing Itanium 2 processor performance.

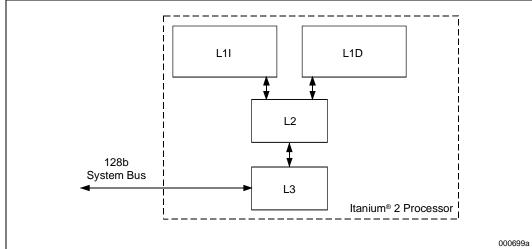

# 2.5 Memory Subsystem

The main system memory is accessed through the 128-bit system bus (refer to Figure 2-5). The system bus is transaction-oriented and pipelined similar to the Itanium processor system bus. The memory subsystem for the Itanium 2 processor contains system bus interface logic, the L1D cache, the L2 cache, the L3 cache, interrupt controller unit, ALAT and TLB.

The Itanium 2 processor supports all non-aligned IA-32 memory accesses. References to memory in Itanium architecture spanning an 8 byte boundary will result in an unaligned fault. To avoid performance degradation associated with unaligned accesses and extra overhead for unaligned data memory fault handlers, aligned memory operands should be used whenever possible.

The L1, L2 and L3 caches are non-blocking. There are separate L1 caches for data and instructions. The L1 data cache is quad ported. The L2 cache is a unified cache and contains both instructions and data. It is quad ported and can be accessed at the full clock speed of the Itanium 2 processor. All ports are used when accessing instructions in L2 cache, but for data requests one can utilize either one, two, three or all of the four ports. When a request to the L2 cache causes a miss, the request is quickly forwarded to the L3 cache.

The integrated external interrupt controller interfaces to the system bus through the external bus logic and receives both external and internal interrupts from the system bus through its memory mapped location.

Figure 2-5. Itanium<sup>®</sup> 2 Processor Cache Hierarchy

#### 2.5.1 L1 Instruction Cache

The Itanium 2 processor L1 instruction (L1I) cache is 16 KB in size. It is a single cycle, non-blocking, dual ported 4-way set-associative cache memory with a 64 byte line size (there is no way prediction). The tag array is dual ported. One port is for instruction fetches, the other port is shared among prefetches, snoops, fills, and column invalidates. The data array is also dual ported to support simultaneous reads (fetches) and fills. The L1I is fully pipelined and can deliver two instruction bundles (six instructions) every clock.

The L1I cache is physically indexed and tagged.

#### 2.5.2 L1 Data Cache

The L1 data cache is four-ported (two loads and two stores), 16 KB in size and is non-blocking. It is organized as 4-way set-associative (no way prediction) with 64 byte line size. It can support two concurrent loads and two stores. The L1 data cache only caches integer data (does not cache floating-point load or semaphore load data). The L1D cache is write-through with no write allocation. The L1D cache is physically indexed and tagged for loads and stores.

#### 2.5.3 Unified L2 Cache

The unified L2 cache memory is four-ported and supports up to four concurrent accesses via banking. The L2 cache is 256 KB, 8-way set-associative with a 128 byte line size, made of 16 byte banks and is non-blocking and out of order. It has a cache read bandwidth of 64 GB per second. The L2 cache implements a write-back with write-allocate policy. It is physically indexed and physically tagged.

In addition to servicing all L1I and L1D cache misses, the L2 handles all floating-point memory accesses (up to four concurrent floating-point loads per clock). All of the Itanium 2 processor's semaphore instructions are also handled exclusively by the L2.

#### 2.5.4 Unified L3 Cache

The on chip L3 cache on the Itanium 2 processor is 1.5 MB or 3 MB in size. It is physically indexed and physically tagged. The L3 cache is single ported, fully pipelined non-blocking cache featuring 12 way set-associative with 128 byte line size. It can support 8 outstanding requests, 7 of which are loads/stores and 1 is for fills. The maximum transfer rate from L3 to core/L1I/L1D or L2 is 32 GB/cycle. The L3 protects both tag and data with single bit correction and double bit detection ECC.

# 2.5.5 The Advanced Load Address Table (ALAT)

A cache structure called the Advanced Load Address Table (ALAT) is used to enable data speculation in the Itanium 2 processor. The ALAT keeps information on speculative data loads issued by the machine and any stores that are aliased with these loads. This structure has 32 entries, is a fully associative array that can handle two loads and two stores per cycle. It can provide aliasing information for the advance load "check" operations.

# 2.5.6 Translation Lookaside Buffers (TLBs)

There are two types of TLBs on the Itanium 2 processor: Data Translation Lookaside Buffer (DTLB) and the Instruction Translation Lookaside Buffer (ITLB). There are two levels of DTLBs in the Itanium 2 processor: a L1 DTLB and a L2 DTLB. Only L1D cache loads depend on the L1 and L2 DTLB hits. Stores and L2/L3 cache hits only depend on the L2 DTLB hits.

TLB misses in either the DTLB or the ITLB are serviced by the hardware page table walker which supports the Itanium instruction set architecture-defined 8B and 32B Virtual Hash Page Table (VHPT) format. VHPT data is only cached on the L2 and L3 caches, not the L1D.

#### 2.5.6.1 The Data TLB (DTLB)

The first level DTLB (DTLB1) performs virtual to physical address translations for load transactions that hit in the L1 cache. It has two read ports and one write port. The TLB contains 32 entries and is fully associative. It supports 4 KB pages, and can also support subsets of larger caches in 4 KB subsections.

The second level DTLB (DTLB2) handles virtual to physical address translations for data memory references during stores, and protection checking on loads. It contains 128 entries and is fully associative and can support architected page sizes from 4 KB to 4 GB. The DTLB2 contains four ports. Of the 128 entries, 64 can be configured as Translation Registers (TR).

#### 2.5.6.2 The Instruction TLB (ITLB)

The first level ITLB (ITLB1) is responsible for virtual to physical address translations to enable instruction transaction hits in the L1I cache. It is dual ported, contains 32 entries and is fully associative. It supports 4 KB pages only.

The second level ITLB (ITLB2) is responsible for virtual to physical address translations for instruction memory references that miss the ITLB1. It contains 128 entries, is fully associative and supports page sizes from 4 KB to 4 GB. Of the 128 entries, 64 can be configured as TR.

# 2.5.7 Cache Coherency

The three-level cache system makes it necessary to maintain the consistency of the data in the different caches. Every read access to a memory address must always provide the most up-to-date data at that address. Since the L1 is write-through it maintains a valid bit. The valid bit indicates whether or not the cache line is valid. The L2 and L3 caches use the MESI protocol to maintain cache coherency.

# 2.5.8 Write Coalescing

For increased performance of uncacheable references to frame buffers, the Write Coalescing (WC) memory type coalesces streams of data writes into a single larger bus write transaction. On the Itanium 2 processor, WC loads are performed directly from memory and not from the coalescing buffers.

On the Itanium 2 processor, a separate 2-entry, 128 byte buffer (WCB) is used for WC accesses exclusively. Each byte in the line has a valid bit. If all the valid bits are true, then the line is said to be full and will be evicted (flushed) by the processor. Line evictions are initiated in a "first-written-first-flushed" order even for partially full lines.

For increased performance to cacheable references to frame buffers or graphic controllers, the Itanium 2 processor allows external agents such as a graphics controller to read a line out of the processor's cache without altering the state of the cache line.

## 2.5.9 Memory Ordering

The Itanium 2 processor implements a relaxed memory ordering model to enhance memory system performance. Memory transactions are ordered with respect to visibility whereby visibility of a transaction is defined as a point in time after which no later transactions may affect its operation.

On the Itanium 2 processor, a transaction is considered visible when it hits the L1D (if the instruction is serviceable by L1D), the L2, or the L3, or when it has reached the visibility point on the system bus.

#### 2.6 IA-32 Execution

The Itanium 2 processor supports IA-32 application binaries. This includes support for running a mix of IA-32 applications and Itanium-based applications on an Itanium-based operating system (OS), in both uniprocessor and multiprocessor configurations. The IA-32 engine is designed to make use of the registers, caches, and execution resources of the EPIC machine. To deliver high performance on legacy binaries, the IA-32 engine dynamically schedules instructions.

# intel® System Bus Overview

This chapter provides an overview of the Itanium 2 processor system bus, bus transactions, and bus signals. The Itanium 2 processor also supports signals not discussed in this section. For a complete signal listing, please refer to the Intel<sup>®</sup> Itanium<sup>®</sup> 2 Processor at 1.0 GHz and 900 MHz Datasheet and Appendix A, "Signals Reference".

#### Signaling on the Itanium® 2 Processor System Bus 3.1

The Itanium 2 processor system bus supports common clock signaling as well as source synchronous data signaling. Section 3.1.1 and Section 3.1.2 describe in detail the characteristics of each type of signaling. The corresponding timing figures use square, triangle, and circle symbols to indicate the point at which signals are driven, received, and sampled, respectively. The square indicates that a signal is driven (asserted or deasserted) in that clock. The triangle indicates that a signal is received on or before that point. The circle indicates that a signal is sampled (observed, latched, captured) in that clock. Black bars indicate zero or more clocks are allowed.

All timing diagrams in this specification show signals as they are asserted or deasserted. There is a one-clock delay in the signal values observed by system bus agents. Any signal names that appear in lowercase letters in brackets {rcnt} are internal signals only, and are not driven to the bus. Internal states change one clock after sampling a bus signal, which is the clock after the bus signal is driven. Uppercase letters that appear in brackets represent a group of signals such as the Request Phase signals [REOUEST]. The timing diagrams sometimes include internal signals to indicate internal states and show how it affects external signals. Internal states change one clock after sampling a bus signal. A bus signal is sampled one clock after the bus signal is driven.

#### 3.1.1 Common Clock Signaling

All signals except the data bus signals on the system bus use a synchronous common clock latched protocol (1x transfer rate). On the rising edge of the bus clock, all agents on the system bus are required to drive their active outputs and sample required inputs. No additional logic is located in the output and input paths between the buffer and the latch stage, thus keeping setup and hold times constant for all bus signals following the latched protocol. The system bus requires that (1) every input be sampled during a valid sampling window on a rising clock edge and, (2) its effect be driven out no sooner than the next rising clock edge. This approach allows one full clock for driving a signal, flight time, and setup as well as at least one full clock at the receiver to compute a response.

Figure 3-1 illustrates the latched bus protocol as it appears on the bus. In later descriptions, the protocol is described as "B# is asserted in the clock after A# is observed asserted," or "B# is asserted two clocks after A# is asserted." Note that A# is asserted in T1, but not observed asserted until T2. A# has one full clock to propagate (indicated by the straight line with arrows) before it is observed asserted. The receiving agent uses T2 to determine its response and asserts B# in T3 i.e. it has one full clock cycle from the time it observes A# asserted (at the rising edge of T2) to the time it computes its response (indicated by the curved line with the single arrow) and drives this response at the rising edge of T3 on B#. Similarly, an agent observes A# asserted at the rising edge of T2, and uses the full T2 clock to compute its response (indicated by the lowermost curved arrow during T2). This response would be driven at the rising edge of T3 (not shown in Figure 3-1) on {c} signals. Although B# is driven at the rising edge of T3, it has the full clock T3 to propagate. B# is observed asserted in T4.

Figure 3-1. Common Clock Latched Protocol

Signals that are driven in the same clock by multiple system bus agents exhibit a "wired-OR glitch" on the electrical low to electrical high transition. To account for this situation, these signal state transitions are specified to have two clocks of settling time when deasserted before they can be safely observed, as shown with B#. The bus signals that must meet this criterion are: BINIT#, HIT#, HITM#, BNR#, TND#, BERR#.

# 3.1.2 Source Synchronous Signaling

The data bus operates with a source synchronous latched protocol (2x transfer rate). The source synchronous latched protocol (refer to Figure 3-2) sends and latches data with strobes to allow very high transfer rates with reasonable signal flight times. The rest of the system bus always uses the common clock latched protocol.

The source synchronous latched protocol operates the data bus at twice the "frequency" of the common clock. Two chunks of data are driven onto the bus in the time it would normally take to drive one chunk. The worst case flight time is similar to the common clock latched protocol, so the second data transfer may be driven before the first is latched. On both the rising edge and 50% point of the bus clock, drivers send new data. On both the 25% point and the 75% point of the bus clock, drivers send centered differential strobes. The receiver captures the data with the strobes deterministically.

Figure 3-2. Source Synchronous Latched Protocol

The driver pre-drives STBp# before driving data. It sends a rising and falling edge on STBp# and STBn# centered with data. The driver must deassert all strobes after the last data is sent. The receiver captures valid data with the difference of both strobe signals, asynchronous to the common clock. Data will be latched into the core within one core-cycle after being captured. A signal synchronous to the common clock (DRDY#) indicates to the receiver that valid data has been sent.

# 3.2 Signal Overview

This section describes the function of various Itanium 2 processor signals. In this section, the signals are grouped according to function. For a complete signal listing, please refer to the *Intel*<sup>®</sup> *Itanium* 2 *Processor at 1.0 GHz and 900 MHz Datasheet*.

# 3.2.1 Control Signals

The control signals, shown in Table 3-1, are used to control basic operations of the processor.

**Table 3-1. Control Signals**

| Signal Function                       | Signal Names |

|---------------------------------------|--------------|

| Positive Phase Bus Clock              | BCLKp        |

| Negative Phase Bus Clock              | BCLKn        |

| Reset Processor and System Bus Agents | RESET#       |

| Power Good                            | PWRGOOD      |

The Positive Phase Bus Clock (BCLKp) input signal is the positive phase of the system bus clock differential pair. It is also referred to as CLK in some of the waveforms in this overview. It specifies the bus frequency and clock period and is used in the signaling scheme. Each processor derives its internal clock from CLK by multiplying the bus frequency by a multiplier determined at configuration. See Chapter 5, "Configuration and Initialization" for further details.

The Negative Phase Bus Clock (BCLKn) input signal is the negative phase of the system bus clock differential pair.

The RESET# signal resets all system bus agents to known states.

**Note:** The RESET# signal itself does not invalidate the internal caches in the Itanium 2 processor. A subsequent PAL call is used to invalidate all internal caches in the Itanium 2 processor. Modified or dirty cache lines are NOT written back. After RESET# is deasserted, each processor begins execution at the power-on reset vector defined during configuration.

The Power Good (PWRGOOD) input signal must be deasserted during power-on and be asserted after RESET# is first asserted by the system.

# 3.2.2 Arbitration Signals

The arbitration signals, shown in Table 3-2, are used to arbitrate for ownership of the bus, a requirement for initiating a bus transaction.

**Table 3-2. Arbitration Signals**

| Signal Function             | Signal Names         |

|-----------------------------|----------------------|

| Symmetric Agent Bus Request | BREQ[3:0]#, BR[3:0]# |

| Priority Agent Bus Request  | BPRI#                |

| Block Next Request          | BNR#                 |

| Lock                        | LOCK#                |

BR[3:0]# are the physical pins of the processor. All processors assert only BR0#. BREQ[3:0]# refers to the system bus arbitration signals among four processors. BR0# of each of the four processors is connected to a unique BREQ[3:0]# signal.

Up to five agents can simultaneously arbitrate for the request bus, one to four symmetric agents (on BREQ[3:0]#) and one priority agent (on BPRI#). Processors arbitrate as symmetric agents, while the priority agent normally arbitrates on behalf of the I/O agents and memory agents. Owning the request bus is a necessary pre-condition for initiating a transaction.

The symmetric agents arbitrate for the bus based on a round-robin rotating priority scheme. The arbitration is fair and symmetric. A symmetric agent requests the bus by asserting its BREQ*n*# signal. Based on the values sampled on BREQ[3:0]#, and the last symmetric bus owner, all agents simultaneously determine the next symmetric bus owner.

The priority agent asks for the bus by asserting BPRI#. The assertion of BPRI# temporarily overrides, but does not otherwise alter the symmetric arbitration scheme. When BPRI# is sampled asserted, no symmetric agent issues another unlocked transaction until BPRI# is sampled deasserted. The priority agent is always the next bus owner.

BNR# can be asserted by any bus agent to block further transactions from being issued to the request bus. It is typically asserted when system resources, such as address or data buffers, are about to become temporarily busy or filled and cannot accommodate another transaction. After bus initialization, BNR# can be asserted to delay the first transaction until all bus agents are initialized.

LOCK# is never asserted or sampled in the Itanium 2 processor system environment.

# 3.2.3 Request Signals

The request signals, shown in Table 3-3, are used to initiate a transaction.

**Table 3-3. Request Signals**

| Signal Function | Signal Names |

|-----------------|--------------|

| Address Strobe  | ADS#         |

| Request         | REQ[5:0]#    |

| Address         | A[49:3]#     |

| Address Parity  | AP[1:0]#     |

| Request Parity  | RP#          |

The assertion of ADS# defines the beginning of the transaction. The REQ[5:0]#, A[49:3]#, AP[1:0]#, and RP# are valid in the clock that ADS# is asserted.

In the clock that ADS# is asserted, the A[49:3]# signals provide an active-low address as part of the request. The low three bits of address are mapped into byte enable signals for 0 to 8 byte transfers. AP[1]# protects the address signals A[49:27]#. AP[0]# protects the address signals A[26:3]#. A parity signal on the system bus is correct if there are an even number of electrically low signals in the set consisting of the protected signals plus the parity signal. Parity is computed using voltage levels, regardless of whether the covered signals are active high or active low.

The Request Parity (RP#) signal protects the request pins REQ[5:0]# and the address strobe, ADS#.

# 3.2.4 Snoop Signals

The snoop signals, shown in Table 3-4, are used to provide snoop results and transaction control to the system bus agents.

Table 3-4. Snoop Signals

| Signal Function                         | Signal Names |

|-----------------------------------------|--------------|

| Purge Global Translation Cache Not Done | TND#         |

| Keeping a Non-Modified Cache Line       | HIT#         |

| Hit to a Modified Cache Line            | HITM#        |

Table 3-4. Snoop Signals (Continued)

| Signal Function              | Signal Names |

|------------------------------|--------------|

| Defer Transaction Completion | DEFER#       |

| Guarantee Sequentiality      | GSEQ#        |

The TND# signal may be asserted by a bus agent to delay completion of a Purge Global Translation Cache (PTC.g) instruction, even after the PTC.g transaction completes on the system bus. Software will guarantee that only one PTC.g instruction is being executed in the system.

The HIT# and HITM# signals are used to indicate that the line is valid or invalid in the snooping agent, whether the line is in the modified (dirty) state in the caching agent, or whether the transaction needs to be extended. The HIT# and HITM# signals are used to maintain cache coherency at the system level.

If the memory agent observes HITM# active, it relinquishes responsibility for the data return and becomes a target for the implicit cache line writeback. The memory agent must merge the cache line being written back with any write data and update memory. The memory agent must also provide the implicit writeback response for the transaction.

If HIT# and HITM# are sampled asserted together, it means that a caching agent is not ready to indicate snoop status, and it needs to extend the transaction.

The DEFER# signal is deasserted to indicate that the transaction can be guaranteed in-order completion. An agent asserting ensures proper removal of the transaction from the In-Order Queue by generating the appropriate response.

The assertion of the GSEQ# signal allows the requesting agent to issue the next sequential uncached write even though the transaction is not yet visible. By asserting the GSEQ# signal, the platform also guarantees not to retry the transaction, and accepts responsibility for ensuring the sequentiality of the transaction with respect to other uncached writes from the same agent.

# 3.2.5 Response Signals

The response signals, shown in Table 3-5, are used to provide response information to the requesting agent.

Table 3-5. Response Signals

| Signal Function           | Signal Names |

|---------------------------|--------------|

| Response Status           | RS[2:0]#     |

| Response Parity           | RSP#         |

| Target Ready (for writes) | TRDY#        |

Requests initiated in the Request Phase enter the In-Order Queue, which is maintained by every agent. The responding agent is responsible for completing the transaction at the top of the In-Order Queue. The responding agent is the agent addressed by the transaction.

For write transactions, TRDY# is asserted by the responding agent to indicate that it is ready to accept write or writeback data. For write transactions with an implicit writeback, TRDY# is asserted twice, first for the write data transfer and then for the implicit writeback data transfer.

The RSP# signal provides parity protection for RS[2:0]#. A parity signal on the system bus is correct if there is an even number of low signals in the set consisting of the covered signals plus the parity signal. Parity is computed using voltage levels, regardless of whether the covered signals are active high or active low.

# 3.2.6 Data Signals

The data response signals, shown in Table 3-6, control the transfers of data on the bus and provide the data path. All data transfers are at the 2x transfer rate.

**Table 3-6. Data Signals**

| Signal Function            | Signal Names              |

|----------------------------|---------------------------|

| Data Ready                 | DRDY#, DRDY_C1#, DRDY_C2# |

| Data Bus Busy              | DBSY#, DRDY_C1#, DRDY_C2# |

| Strobe Bus Busy            | SBSY#, SBSY_C1#, SBSY_C2# |

| Data                       | D[127:0]#                 |

| Data ECC Protection        | DEP[15:0]#                |

| Positive phase Data Strobe | STBp[7:0]#                |

| Negative phase Data Strobe | STBn[7:0]#                |

DRDY# indicates that valid data is on the bus and must be latched. The data bus owner asserts DRDY# for each clock in which valid data is to be transferred. DRDY# can be deasserted to insert wait states in the Data Phase.

DBSY# holds the data bus before the first DRDY# and between DRDY# assertions for a multiple clock data transfer. DBSY# need not be asserted for single clock data transfers.

SBSY# holds the strobe bus before the first DRDY# and between DRDY# assertions for a multiple clock data transfer. SBSY# must be asserted for all data transfers on the bus.

Each of the data bus control signals DBSY#, DRDY#, and SBSY# are replicated on the Itanium 2 processor system bus to enable partitioning of data path chips in the system agents. Two copies of DBSY#, DRDY#, and SBSY# signals are output-only and the third copy serves as both input as well as output.

The D[127:0]# signals provide a 128-bit data path between agents. For partial transfers, BE[7:0]# and A[4:3]# determine which bytes of the data bus contain valid data.

The DEP[15:0]# signals provide optional ECC (error correcting code) protection for D[127:0]#. DEP[15:0]# provides valid ECC protection for the entire data bus on each clock, regardless of which bytes are enabled.

STBp[7:0]# and STBn[7:0]# (and DRDY#) are used to transfer data at the 2x transfer rate with the source synchronous latched protocol. The agent driving the data transfer drives the strobes with the corresponding data and ECC signals. The agent receiving the data transfer uses the strobes to capture valid data. Each strobe pair is associated with sixteen data signals and two ECC signals as shown in Table 3-7.

Table 3-7. STBp[7:0]# and STBn[7:0]# Associations

| Strobe Signals     | Data Signals | ECC Signals |

|--------------------|--------------|-------------|

| STBp[7]#, STBn[7]# | D[127:112]#  | DEP[15:14]# |

| STBp[6]#, STBn[6]# | D[111:96]#   | DEP[13:12]# |

| STBp[5]#, STBn[5]# | D[95:80]#    | DEP[11:10]# |

| STBp[4]#, STBn[4]# | D[79:64]#    | DEP[9:8]#   |

| STBp[3]#, STBn[3]# | D[63:48]#    | DEP[7:6]#   |

| STBp[2]#, STBn[2]# | D[47:32]#    | DEP[5:4]#   |

| STBp[1]#, STBn[1]# | D[31:16]#    | DEP[3:2]#   |

| STBp[0]#, STBn[0]# | D[15:0]#     | DEP[1:0]#   |

## 3.2.7 Defer Signals

The defer signals, shown in Table 3-8, are used by a deferring agent to complete a previously deferred transaction. Any deferrable transaction (DEN# asserted) may use the deferred response signals, provided the requesting agent supports a deferred response (DPS# asserted).

#### Table 3-8. Defer Signals

| Signal Function | Signal Names |

|-----------------|--------------|

| ID Strobe       | IDS#         |

| Transaction ID  | ID[9:0]#     |

IDS# is asserted to begin the deferred response. ID[9:0]# returns the ID of the deferred transaction that was sent on DID[9:0]#. Please refer to Appendix A, "Signals Reference" for further details.

# 3.2.8 Error Signals

Table 3-9 lists the error signals on the system bus.

#### Table 3-9. Error Signals

| Signal Function    | Signal Names |

|--------------------|--------------|

| Bus Initialization | BINIT#       |

| Bus Error          | BERR#        |

| Thermal Trip       | THRMTRIP#    |

| Thermal Alert      | THRMALERT#   |

BINIT# is used to signal any bus condition that prevents reliable future operation of the bus. BINIT# assertion can be enabled or disabled as part of the power-on configuration register (see Chapter 5, "Configuration and Initialization"). If BINIT# assertion is disabled, BINIT# is never asserted and the error recovery action is taken only by the processor detecting the error.

BINIT# sampling can be enabled or disabled at power-on reset. If BINIT# sampling is disabled, BINIT# is ignored and no action is taken by the processor even if BINIT# is sampled asserted. If BINIT# sampling is enabled and BINIT# is sampled asserted, all processor bus state machines are reset. All agents reset their rotating ID for bus arbitration, and internal state information is lost. Cache contents are not affected. BINIT# sampling and assertion must be enabled for proper processor error recovery.

A machine-check abort is taken for each BINIT# assertion, configurable at power-on.

BERR# is used to signal any error condition caused by a bus transaction that will not impact the reliable operation of the bus protocol (for example, memory data error or non-modified snoop error). A bus error that causes the assertion of BERR# can be detected by the processor or by another bus agent. BERR# assertion can be enabled or disabled at power-on reset. If BERR# assertion is disabled, BERR# is never asserted. If BERR# assertion is enabled, the processor supports two modes of operation, configurable at power-on (refer to section 5.2.6 and 5.2.7 for further details). If BERR# sampling is disabled, BERR# assertion is ignored and no action is taken by the processor. If BERR# sampling is enabled, and BERR# is sampled asserted, the processor core is signaled with the machine check exception.

A machine check exception is taken for each BERR# assertion, configurable at power-on.

THRMTRIP# is the Thermal Trip signal. The Itanium 2 processor protects itself from catastrophic overheating by using an internal thermal sensor. This sensor is set well above the normal operating temperature to ensure that there are no false trips. Data will be lost if the processor goes into thermal trip. This is signaled to the system by the assertion of the THRMTRIP# pin. Once asserted, the signal remains asserted until RESET# is asserted by the platform. There is no hysteresis built into the thermal sensor itself; as long as the case temperature drops below specified maximum, a RESET# pulse will reset the processor.

A thermal alert open-drain signal, indicated to the system by the THRMALERT# pin. The signal is asserted when the measured temperature from the processor thermal diode equals or exceeds the temperature threshold data programmed in the high-temp or low-temp registers on the sensor. This signal can be used by the platform to implement thermal regulation features such as generating an external interrupt to tell the operating system that the processor core is heating up.

# 3.2.9 Execution Control Signals

The execution control signals, shown in Table 3-10, contains signals that change the execution flow of the processor.